Уральский государственный архитектурно-художественный университет Национальный исследовательский Томский государственный университет Уральский федеральный университет имени первого Президента России Б.Н. Ельцина

## НОВЫЕ ИНФОРМАЦИОННЫЕ ТЕХНОЛОГИИ В ИССЛЕДОВАНИИ СЛОЖНЫХ СТРУКТУР

МАТЕРИАЛЫ ОДИННАДЦАТОЙ МЕЖДУНАРОДНОЙ КОНФЕРЕНЦИИ 6–10 июня 2016 г. на вход детектора на его выходах реализуется сигнал (10). Появление (00, 01, 11) означает, что на вход поступил набор не из множества  $\hat{W}_n^m$ . Для получения структурной реализации детектора использовались встроенные методы синтеза и оптимизации в системе ABC, разработанной в университете Беркли. Компьютерные эксперименты показали, что монотонный детектор для подмножества равновесных кодов требует меньших затрат по сравнению с методом, реализующим функцию детектора по ее совершенной ДНФ, и ранее предложенным методом построения монотонного детектора.

## СИНТЕЗ ОТКАЗОУСТОЙЧИВЫХ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ ДЛЯ НЕИСПРАВНОСТЕЙ ЗАДЕРЖЕК ПУТЕЙ\*

С.А. Останин, А.Ю. Матросова, И.Е. Кириенко, Е.А. Николаева

Национальный исследовательский Томский государственный университет, Томск, Россия {mau11, sergeiostanin}@yandex.ru, irina.kirienko@sibmail.com, nikolaeve-ea@yandex.ru

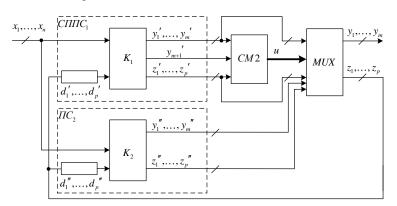

В данной работе предлагается архитектура построения отказоустойчивых последовательностных схем, состоящая из самопроверяемой схемы, «обычной» схемы (схемы без дополнительных свойств, реализующей основную функциональность), схемы, реализующей сложение по модулю 2 и мультиплексора для одиночных неисправностей задержек путей, кратковременных или перемежающихся. Предложенная архитектура представлена на рис. 1.

Рис. 1. Отказоустойчивая схема

$C\Pi\Pi C_1$  — самопроверяемая последовательностная схема, поведение которой задано STG-описанием, т.е. входной и выходной алфавиты закодированы, а внутренние состояния нет. Для кодирования внутренних состояний предлагается использовать равновесный код с последующим описанием поведения комбинационной части ( $K_1$ ) в виде системы полностью определенных частично монотонных булевых функций. Частичная монотонность достигается за счет дополнительной минимизации функций системы заменой нулевых значений переменных состояний на

значение «—». Комбинационная часть  $K_1$  имеет следующие выходы:  $y_1'$ , ...,  $y_m'$  соответствуют выходам последовательностной схемы,  $y_{m+1}'$  обеспечивает четность (или нечетность) на выходах  $K_1$ ,  $z_1'$ , ...,  $z_p'$  соответствуют линиям обратных связей. В качестве метода структурного синтеза используется многоуровневый метод синтеза, основанный на делении ДНФ с дальнейшим выделением подсхем и покрытием этих подсхем графами, представляющими функции элементов реального базиса (в нашем случае двухвходовые элементы NAND и NOT).

$\Pi C_2$  — последовательностная схема, реализуется аналогично  $C\Pi\Pi C_1$ , за исключением дополнительного выхода, обеспечивающего четность (нечетность); он в данной схеме отсутствует.

CM2 — схема, реализующая функцию «сложение по модулю 2» для выходов комбинационной части  $K_1$ . На выходе u схемы CM2 реализуется единичный сигнал, если булев вектор, поступивший с выходов  $K_1$ , имеет нечетный вес, и нулевой сигнал в случае четного веса. В общем случае структурная реализация схемы CM2 может быть произвольной.

MUX — схема мультиплексора, на вход которого подается управляющий сигнал (u) и сигналы с данными  $(y'_1,\ldots,y'_m,z'_1,\ldots,z_p',y''_1,\ldots,y''_m,z''_1,\ldots,z''_p)$ . Если на выходах  $K_1$  мы обеспечиваем четность (нечетность), то при поступлении сигнала u=0 (u=1) мультиплексор соединяет входы  $y'_1,\ldots,y'_m,z'_1,\ldots,z'_p$  с выходами схемы в целом  $y_1,\ldots,y_m,z_1,\ldots,z_p$ ; когда управляющий сигнал u=1 (u=0), то мультиплексор соединяет входы  $y''_1,\ldots,y''_m,z''_1,\ldots,z''_p$  с выходами  $y_1,\ldots,y_m,z_1,\ldots,z_p$ .

Проанализируем отказоустойчивые свойства предложенной архитектуры. Прежде всего, будем предполагать, что в текущий момент времени может быть неисправна только одна схема (СППС $_1$ ,  $\Pi C_2$ , CM2 или MUX). Ограничимся кратковременными и перемежающимися неисправностями. Допускается появление очередной неисправности только после исчезновения всех последствий от предыдущей неисправности.

.

<sup>\*</sup> Работа выполнена при частичной поддержке грантом Российского научного фонда № 14-19-00218.

Рассмотрим допустимый класс неисправностей схемы  $C\Pi\Pi C_1$ . Этот класс содержит все одиночные неисправности задержек путей, т.е. задержки появляются на одном пути, ведущем от одного входа к одному выходу. Такое допущение имеет место быть, т.к. неисправности проявляют себя временно, и вероятность накопления неисправностей низкая. При поступлении теста изменится только один выход, что приведет к изменению четности и будет обнаружено схемой CM2. В этом случае мультиплексор будет получать корректные сигналы с выходов комбинационной части схемы  $\Pi C_2$ .

Допустимый класс неисправностей схемы мультиплексора (MUX) включает неисправности, приводящие к изменению переключений между соответствующими входами ( $y'_1, \ldots, y'_m, z_1', \ldots, z_p'$ ) и ( $y''_1, \ldots, y''_m, z''_1, \ldots, z''_p$ ). Такие неисправности не повлияют на корректное функционирование схемы в целом, т.к.  $K_1$  и  $K_2$  исправны и на их выходах реализуются корректные значения.

Для схем  $\Pi C_2$  и CM2 можно рассматривать произвольные неисправности, не ограничиваясь каким-либо классом, т.к. неисправности в этих схемах не влияют на корректное функционирование схемы в целом.

Таким образом, нами предложена архитектура отказоустойчивой последовательностной схемы относительно одиночных неисправностей задержек путей. Ограничение на класс допустимых неисправностей определяется неисправностями схемы  $C\Pi\Pi C_1$ . Данное ограничение позволило сократить аппаратурную избыточность за счет использования только одного дополнительного выхода для  $C\Pi\Pi C_1$ . Также в данной архитектуре вместо самотестируемого детектора используется простая схема, реализующая сложение по модулю 2.

## СРАВНЕНИЕ КОДА БЕРГЕРА И МОДИФИЦИРОВАННОГО КОДА С СУММИРОВАНИЕМ ВЗВЕШЕННЫХ ПЕРЕХОДОВ В СИСТЕМАХ ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ

В.В. Сапожников, Вл.В. Сапожников, Д.В. Ефанов, В.В. Дмитриев, М.Р. Черепанова

Петербургский государственный университет путей сообщения Императора Александра I, Санкт-Петербург, Россия TrES-4b@yandex.ru

При синтезе надежных дискретных устройств автоматики и вычислительной техники часто используют методы функционального контроля логических компонентов без памяти [1, 2]. Применение функционального контроля позволяет косвенно по результатам вычислений оценивать техническое состояние контролируемого объекта. Эффективным является использование кодов с суммированием для решения задачи организации системы функционального контроля. Получаемая на их основе система функционального контроля зачастую является более простой, чем система дублирования, однако не всегда возможно построение системы со 100%-ным обнаружением одиночных неисправностей на выходах логических элементов во внутренней структуре. Для реализации данного свойства требуется специальное преобразование топологии контролируемого объекта [3].

При построении систем функционального контроля используется ключевое свойство классического кода с суммированием, или кода Бергера [4], — возможность обнаружения 100% монотонных искажений в информационных векторах. Как показано в [3], для построения контролепригодной структуры требуется увеличение показателя сложности технической реализации самого контролируемого объекта всего на 15,65%. Это число может быть уменьшено за счет применения модифицированных кодов с суммированием и разработки соответствующих алгоритмов реконфигурации структур контролируемых логических схем.

В работе исследуются свойства одной из модификаций кода с суммированием, основанной на принципе взвешивания переходов между разрядами [5], занимающими соседние позиции в информационных векторах кодовых слов и последующих преобразованиях с суммарным весом так называемых активных переходов. Переход называется активным, если выполняется следующее соотношение:  $t_{i,i+1} = f_i \oplus f_{i+1} = 1$ , где  $f_i - i$ -й разряд в информационном векторе,  $f_{i+1} = f_i \oplus f_{i+1} = 1$ , где  $f_i = i$ -й разряд в информационном векторе, а  $f_{i,i+1} = f_i \oplus f_{i+1} = 1$ , где  $f_i = i$ -й разряд в информационными разрядами выбираются из множества  $w_{i,i+1} \in \left\{2^0; 2^1; \ldots; 2^{m-1}\right\}$ . Получаемый суммарный вес является только первым шагом построения кода — получается так называемый «промежуточный» код [6]. Следующие шаги модификации связаны с применением модульного принципа представления суммарного веса и так называемой «сдвиговой» функции, а также с серией перестановок получаемых весов информационных векторов между собой по определенным правилам [7]. Такой подход к построению кода позволяет повысить эффективность обнаружения ошибок в информационных векторах и, соответственно, в векторе рабочих функций контролируемой схемы при сравнительно небольших затратах на реализацию системы функционального контроля.